- 您现在的位置:买卖IC网 > Sheet目录344 > MR25H10CDF (Everspin Technologies Inc)IC MRAM 1MBIT 40MHZ 8DFN

�� �

�

�

�MR25H10�

�SPI� COMMUNICATIONS� PROTOCOL�

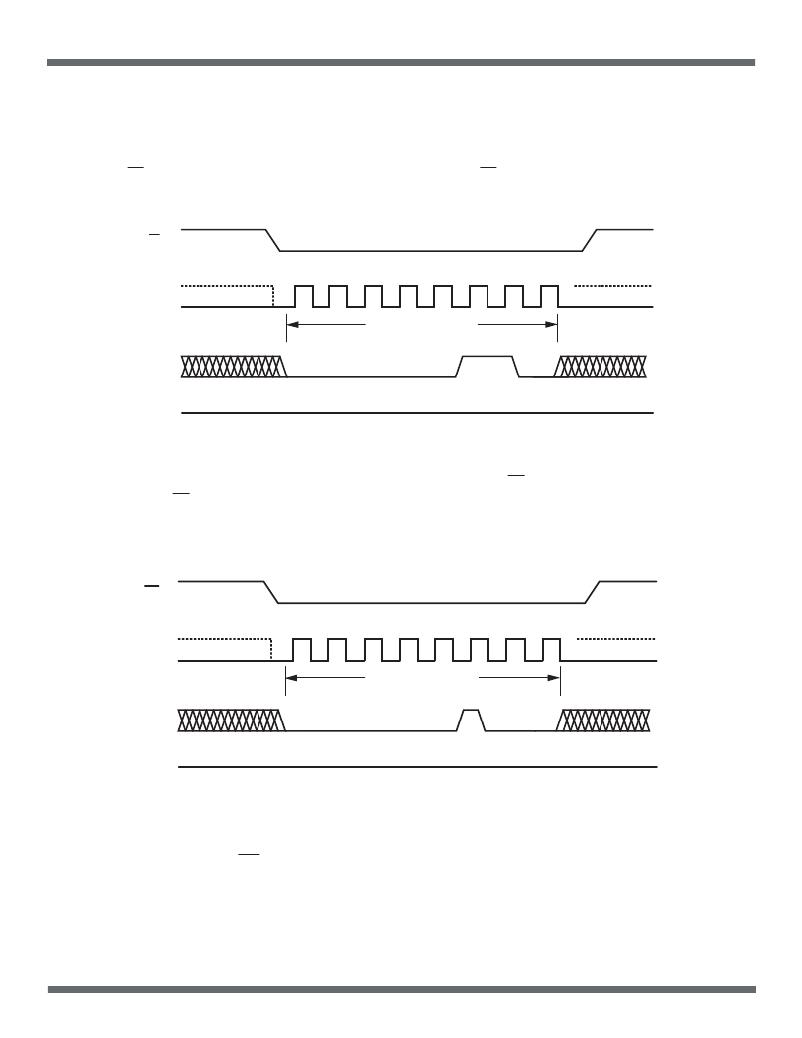

�Write� Enable� (WREN)�

�The Write Enable (WREN) command sets the Write Enable Latch (WEL) bit in the status register to 1. The �

�WEL bit must be set prior to writing in the status register or the memory. The WREN command is entered �

�by driving CS low, sending the command code, and then driving CS high.�

�Figure� 2.2� WREN�

�CS�

�Mode� 3�

�0�

�1�

�2�

�3�

�4�

�5�

�6�

�7�

�Mode� 3�

�SCK�

�Mode� 0�

�Instruction� (06h)�

�Mode� 0�

�SI�

�0�

�0�

�0�

�0�

�0�

�1�

�1�

�0�

�SO�

�High� Impedance�

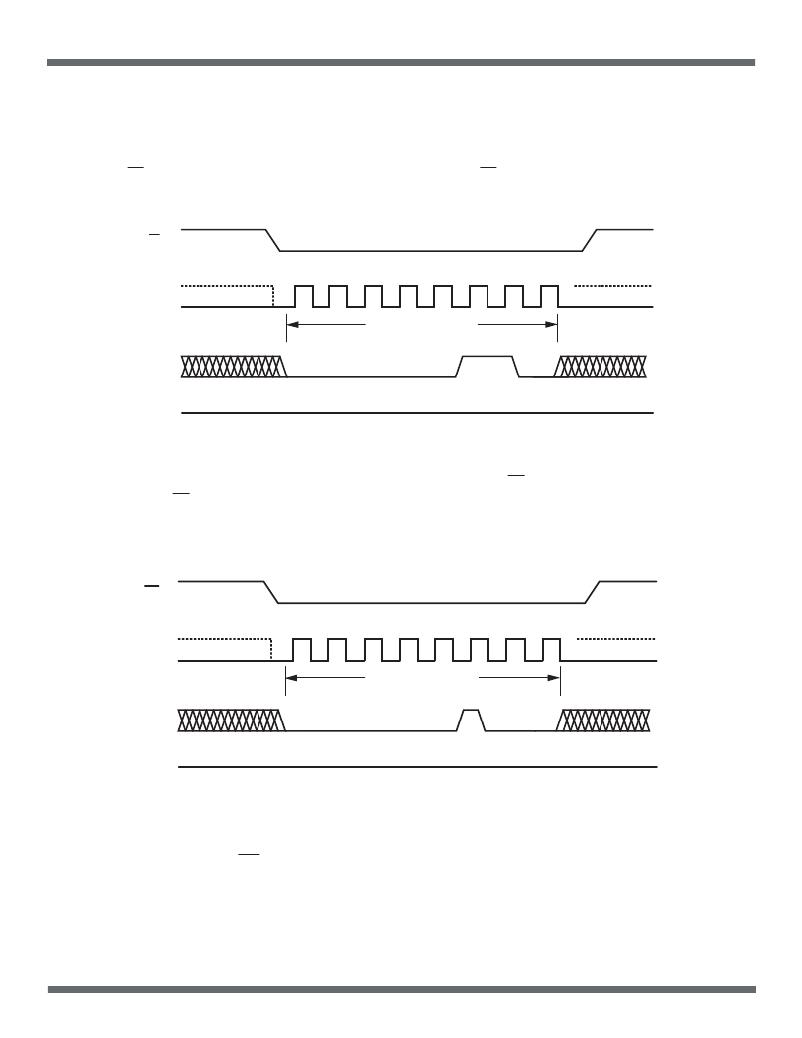

�Write� Disable� (WRDI)�

�The Write Disable (WRDI) command resets the WEL bit in the status register to 0. This prevents writes to �

�status register or memory. The WRDI command is entered by driving CS low, sending the command code, �

�and then driving CS high.�

�The WEL bit is reset to 0 on power-up or completion of WRDI.�

�Figure� 2.3� WRDI�

�CS�

�Mode� 3�

�0�

�1�

�2�

�3�

�4�

�5�

�6�

�7�

�Mode� 3�

�SCK�

�Mode� 0�

�Instruction� (04h)�

�Mode� 0�

�SI�

�0�

�0�

�0�

�0�

�0�

�1�

�0�

�0�

�SO�

�High� Impedance�

�Write� Status� Register� (WRSR)�

�The Write Status Register (WRSR) command allows new values to be written to the Status Register. The �

�WRSR command is not executed unless the Write Enable Latch (WEL) has been set to 1 by executing a �

�WREN command while pin WP and bit SRWD correspond to values that make the status register writable �

�as seen in table 2.4. Status Register bits are non-volatile with the exception of the WEL which is reset to 0 �

�upon power cycling.�

�Copyright� ?� Everspin� Technologies� 2013�

�6�

�MR25H10� Rev.� 9,� 4/2013�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MR25H256CDF

IC MRAM 256KBIT 40MHZ 8DFN

MR25H40CDF

IC MRAM 4MBIT 40MHZ 8DFN

MR2A08AMYS35R

IC MRAM 4MBIT 35NS 44TSOP

MR2A16ATS35CR

IC MRAM 4MBIT 35NS 44TSOP

MR2A16AVMA35R

IC MRAM 4MBIT 35NS 48BGA

MR4A08BCYS35R

IC MRAM 16MBIT 35NS 44TSOP

MRJ-5385-01

CONN RCPT 8POS 2GRN 1PORT PCB

MRJ548501

CONN MOD JACK 8P8C R/A GRN/GRN

相关代理商/技术参数

MR25H10CDFR

功能描述:NVRAM 1Mb 3.3V 128Kx8 Serial MRAM RoHS:否 制造商:Maxim Integrated 数据总线宽度:8 bit 存储容量:1024 Kbit 组织:128 K x 8 接口类型:Parallel 访问时间:70 ns 电源电压-最大:5.5 V 电源电压-最小:4.5 V 工作电流:85 mA 最大工作温度:+ 70 C 最小工作温度:0 C 封装 / 箱体:EDIP 封装:Tube

MR25H10MDC

功能描述:NVRAM 1Mb 3V 128Kx8 Serial MRAM

RoHS:否 制造商:Maxim Integrated 数据总线宽度:8 bit 存储容量:1024 Kbit 组织:128 K x 8 接口类型:Parallel 访问时间:70 ns 电源电压-最大:5.5 V 电源电压-最小:4.5 V 工作电流:85 mA 最大工作温度:+ 70 C 最小工作温度:0 C 封装 / 箱体:EDIP 封装:Tube

MR25H10MDCR

功能描述:NVRAM 1Mb 3V 128Kx8 Serial MRAM

RoHS:否 制造商:Maxim Integrated 数据总线宽度:8 bit 存储容量:1024 Kbit 组织:128 K x 8 接口类型:Parallel 访问时间:70 ns 电源电压-最大:5.5 V 电源电压-最小:4.5 V 工作电流:85 mA 最大工作温度:+ 70 C 最小工作温度:0 C 封装 / 箱体:EDIP 封装:Tube

MR25H10MDF

功能描述:NVRAM 1Mb 3.3V 128Kx8 SPI Pre-Qual Sample MRAM RoHS:否 制造商:Maxim Integrated 数据总线宽度:8 bit 存储容量:1024 Kbit 组织:128 K x 8 接口类型:Parallel 访问时间:70 ns 电源电压-最大:5.5 V 电源电压-最小:4.5 V 工作电流:85 mA 最大工作温度:+ 70 C 最小工作温度:0 C 封装 / 箱体:EDIP 封装:Tube

MR25H10MDFR

功能描述:NVRAM 1Mb 3.3V 128Kx8 SPI Pre-Qual Sample MRAM RoHS:否 制造商:Maxim Integrated 数据总线宽度:8 bit 存储容量:1024 Kbit 组织:128 K x 8 接口类型:Parallel 访问时间:70 ns 电源电压-最大:5.5 V 电源电压-最小:4.5 V 工作电流:85 mA 最大工作温度:+ 70 C 最小工作温度:0 C 封装 / 箱体:EDIP 封装:Tube

MR25H256CDC

功能描述:NVRAM 256Kb 3V 32Kx8 Serial MRAM

RoHS:否 制造商:Maxim Integrated 数据总线宽度:8 bit 存储容量:1024 Kbit 组织:128 K x 8 接口类型:Parallel 访问时间:70 ns 电源电压-最大:5.5 V 电源电压-最小:4.5 V 工作电流:85 mA 最大工作温度:+ 70 C 最小工作温度:0 C 封装 / 箱体:EDIP 封装:Tube

MR25H256CDCR

功能描述:NVRAM 256Kb 3V 32Kx8 Serial MRAM

RoHS:否 制造商:Maxim Integrated 数据总线宽度:8 bit 存储容量:1024 Kbit 组织:128 K x 8 接口类型:Parallel 访问时间:70 ns 电源电压-最大:5.5 V 电源电压-最小:4.5 V 工作电流:85 mA 最大工作温度:+ 70 C 最小工作温度:0 C 封装 / 箱体:EDIP 封装:Tube

MR25H256CDF

功能描述:NVRAM 256Kb 3.3V 32Kx8 Serial MRAM

RoHS:否 制造商:Maxim Integrated 数据总线宽度:8 bit 存储容量:1024 Kbit 组织:128 K x 8 接口类型:Parallel 访问时间:70 ns 电源电压-最大:5.5 V 电源电压-最小:4.5 V 工作电流:85 mA 最大工作温度:+ 70 C 最小工作温度:0 C 封装 / 箱体:EDIP 封装:Tube